✨ 들어가기전

⚙️ 순차 논리 회로 (Sequential Logic Circuit)

🔖 사진자료

정보통신기술용어해설 순서회로

- 순차 논리 회로는 순서 논리 회로라고도 부른다.

- 현재의 입력값에 따라 출력이 결정되는 논리 회로이다.

- 순서 논리 회로는 조합 논리 회로와 기억 소자로 구성된다.

- 기억소자의 출력은 조랍 논리 회로 입력에 연결되어 궤환(Feedback)된다. 따라서 순차 논리 회로는 현재의 입력 상태뿐 아니라 이전의 출력에도 영향을 받는다.

🤔 여기서 잠깐! 궤환(feedback)이란?

- 한국말로는 되먹임이라고 한다.

- 출력 결과가 다시 들어오는 것을 말한다. 즉, 출력이 다시 입력이된다.

순차 논리 회로의 구성은 다음과 같다.

⚙️ 순차 논리 회로 특징

- 순차 논리 회로는 외부로부터 입력과 이전의 출력 상태에 따라 출력이 결정되는 회로이다.

- 기억 기능이 존재한다.

- 플립-플롭(flip-flop)과 논리 게이트로 구성된다.

- 신호의 타이밍에 따라 동기식(클록 관여O)과 비동기식(클록 관여X)으로 나뉜다.

- 대표적인 순차 논리 회로에는 플립플롭, 카운터, 레지스터, RAM 등이 있다.

⚙️ 비동기식과 동기식 순차 논리 회로

- 비동기식 순차 논리 회로

- 순차 논리회로가 규칙적인 시간에 관계없이 입력신호가 입력되면 곧바로 출력하는 회로

- 대표적인 회로 : 래치(latch) 회로

- 동기식 순차 논리 회로

- 클록펄스(clock pulse)가 신호를 입력하기 전에 입력에 입력된 신호에 동작하지 않다가 동작 클록 펄스 신호가 입력되는 순간에 입력에 대한 출력을 내보내는 회로이다. 즉, 클록펄스가 입력되면 출력한다.

- 대표적인 회로 : 플립-플롭(flip-flop)

⚙️ 에지 트리거(edge trigger)

플립플롭 회로등을 동작시킬 때 트리거 신호의 논리 레벨 변화에 의해서 동작하는 것을 에지 트리거라 한다.

- 상승 에지(rising edge) : 0 → 1로 상승

- 하강 에지(falling edge) : 1 → 0로 하강

🖥️ 시간 표현과 상태 기억

⚙️ 신호의 성질

- 곡선 형태의 신호 그래프

마루와 마루 또는 골과 골 사이의 거리를 파장이라 한다.

- 주기 : 왕복 운동이 1번 이루어지는 기간

- 주파수 : 주파수 = 진동수, 1초 동안 신호가 몇 번 진동을 했는지를 의미

📌 발진자

🔖 참고자료

전자 쟁이의 이런 저런 지식 세상

오실레이터 (Oscillator) 한글로는 발진자 또는 발진기라고 불리는 소자는 전자회로에서 반복 적인 또는 주기적인 신호를 생성하는 소자로 클럭을 발생시킨다거나 전파를 발생시키는 등의 기능을 하는 소자이다. 위에 그림 처럼 소신호로 주파수를 발생하는 단일 또는 복합 소자도 있고 회로를 구성해서 특정 신호를 만드는 방법 또 있다.

오실레이터는 대표적으로 RC 오실레이터와 크리스탈 오실레이터, 세라믹 오실레이터가 있다. 여기서 RC 오실레이터는 회로를 이용하여 발진하는 방법이고 크리스탈과 세라믹은 소재를 진동시켜서 얻는 공명으로 주파수를 만든다.

📌 클록 펄스(Clock Pulse)

컴퓨터 등의 디지털 시스템에서 동일한 시스템 내에서 동작하는 각 구성요소의 모든 동작을 동기화(Synchronize)하기 위해 사용하는 전자적인 펄스를 말한다.

클록 펄스는 수정 발진자(crystal oscillator)의 규칙적인 진동에 의해 발생하는 일정한 간격을 갖는 전자적 펄스인데, 컴퓨터의 시스템 클록(CPU 클록)은 이 펄스를 타이밍 펄스 또는 디지털 신호로 사용하여 시스템 내의 각 장치와 회로의 모든 동작을 동기화한다. 클록 펄스의 발생 주기(cycle)를 클록 속도 또는 클록 주파수라고 한다.

📌 래치(Latch)

- 기억 요소와 궤환(feedback) 기능이 있다.

- 클록 펄스에 사용하지 않는 비동기식 비동기식 쌍안정 순차 논리 회로이다.

- 2개씩의 NOR 게이트나 NAND 게이트를 사용하여 구성한다.

- NOR 게이트나 NAND 게이트의 하나의 입력은 반대편의 출력이 입력되는 서로 교차 결합 형태로 궤환을 구성한다.

📑 래치 종류

- SR 래치 (NOR형, NAND형)

- D 래치

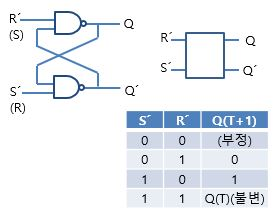

⚙️ S-R 래치?

- 입력 : R(Reset), S(Set)

- 출력 : Q, Q' → 출력값은 서로 반대의 값(보수)이 되어야 정상

⚙️ S-R 래치 : NOR 게이트 래치

🔖 사진자료

정보통신기술용어해설 S-R래치

NOR 게이트는 OR 게이트의 부정이다. 즉, NOR 게이트는 입력이 하나라도 1이면 출력은 0이되고, 모든 입력이 0일 때만 출력은 1이 된다.

- 불변 : 값 유지

- 부정(불능) : 금지

⚙️ S-R 래치 : NAND 게이트 래치

🔖 사진자료

정보통신기술용어해설 S-R래치

NAND 게이트는 AND 게이트의 부정이다. 즉, NAND 게이트는 입력이 하나라도 0이면 출력이 1이 되고, 모든 입력이 1일 때만 출력은 0이 된다.

NAND 래치는 NOR 래치와 반대로 모든 입력이 0일 때 금지이고 모든 입력이 1일 때 불변(값 유지)이다.

- 불변 : 값 유지

- 부정(불능) : 금지

📌 플립플롭(Flip-Flop)

플립플롭은 입력이 변해도 클록이 변하지 않으면 출력이 변하지 않는다. 이와 같이 클록이 있을 때만 동작하는 RS 래치 회로를 RS 플립플롭이라 한다.

클록이 0에서 1로 변하는 것을 상승 에지 또는 정 에지(positive edge)라 하고, 1에서 0으로 변하는 것을 하강 에지 또는 부 에지(negative edge)라 한다.

📑 플립플롭 종류

- SR 플립플롭

- JK 플립플롭

- D 플립플롭

- T 플립플롭

- 주종 플립플롭

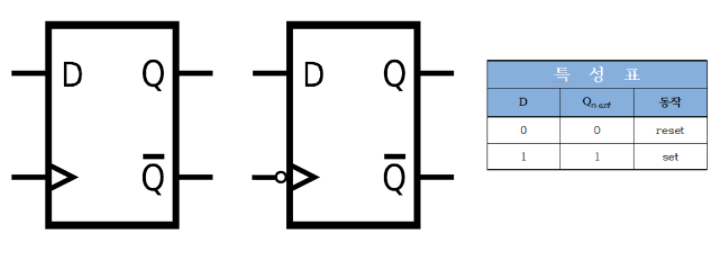

⚙️ D 플립플롭

🔖 참고자료

EBOO

D는 입력 신호를 지연(delay)시키는 의미이다. 입력 상태를 클록 펄스에 의해 일정 시간만큼 출력에 늦게 전달할 때 사용된다. D 플립플롭은 1개의 입력(D)과 2개의 출력(Q, Q')으로 구성된다.

D 플립플롭은 NOT 게이트와 RS 플립플롭 또는 JK 플립플롭으로 구성할 수 있다.

'항해99 > cs 스터디자료' 카테고리의 다른 글

| 프론트엔드 개발자 기술면접 인터뷰 질문 -2022.02.04.FRI (0) | 2022.02.04 |

|---|---|

| 한 권으로 읽는 컴퓨터 구조와 프로그래밍 -2022.01.28.FRI (0) | 2022.01.28 |

| 한 권으로 읽는 컴퓨터 구조와 프로그래밍 -2022.01.26.WED (0) | 2022.01.26 |

| 한 권으로 읽는 컴퓨터 구조와 프로그래밍 -2022.01.25.THU (0) | 2022.01.25 |

| 한 권으로 읽는 컴퓨터 구조와 프로그래밍 -2022.01.24.MON (0) | 2022.01.24 |